LF48212

Description

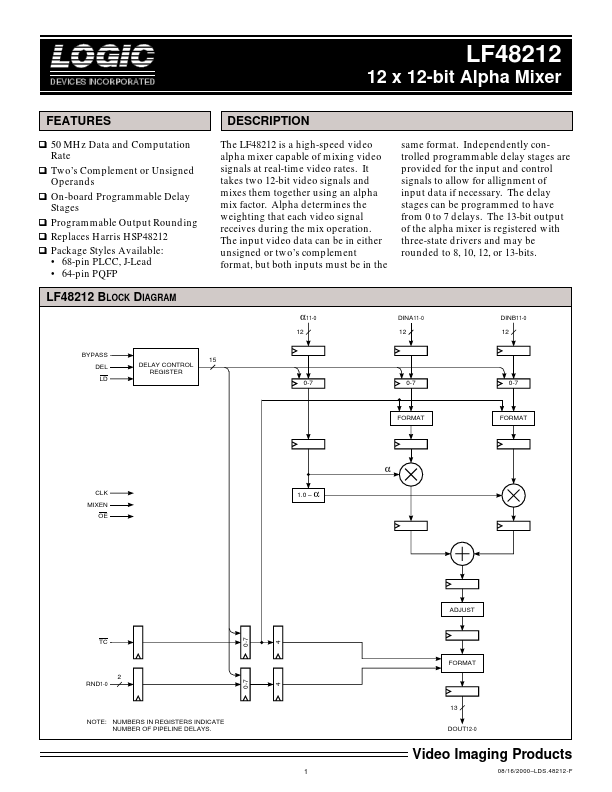

The LF48212 is a high-speed video alpha mixer capable of mixing video signals at real-time video rates. It takes two 12-bit video signals and mixes them together using an alpha mix factor.

Key Features

- 68-pin PLCC, J-Lead

- ALPHA MIX INPUT FORMAT SIGNAL DEFINITIONS Power VCC and GND +5 V power supply. All pins must be connected. Clock CLK

- Load Strobe The rising edge of LD latches the data on DEL into the Delay Control Register. BYPASS